Constructive Computer Architecture

### Modules with Guarded Interfaces

Arvind

Computer Science & Artificial Intelligence Lab.

Massachusetts Institute of Technology

#### Guarded interfaces

Make the life of the programmers easier: Include some checks (readyness, fullness, ...) in the method definition itself, so that the user does not have to test the applicability of the method from outside

#### Guarded Interface:

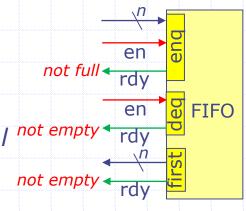

- Every method has a guard (rdy wire)

- The value returned by a method is meaningful only if its guard is true

- Every action method has an enable signal (en wire) and it can be invoked (en can be set to true) only if its guard is true

```

interface Fifo#(numeric type size, type t);

method Action enq(t x);

method Action deq;

method t first;

endinterface

interface roughly size, type t);

method Action enq(t x);

roty wires are

implicit

```

http://csg.csail.mit.edu/6.175

## One-Element FIFO Implementation with guards

```

module mkFifo (Fifo#(1, t));

Reg#(t) d <- mkRegU;

Reg#(Bool) v <- mkReg(False);</pre>

method Action enq(t x), if (!v);

not full ◆ rdy

v <= True; d <= x;

not empty en rdy

FIFO

endmethod

method Action deq if (v);

v <= False;

endmethod

Notice, no semicolon turns

method t first if (v);

the if into a guard

return d;

endmethod

endmodule

```

http://csg.csail.mit.edu/6.175

### Rules with guards

Like a method, a rule can also have a guard

```

rule foo (p);

begin x1 <= e1; x2 <= e2 end

endrule</pre>

```

guard

No if before the guard for rules!

- A rule can execute only if it's guard is true,

i.e., if the guard is false the rule has no effect

- True guards can be omitted

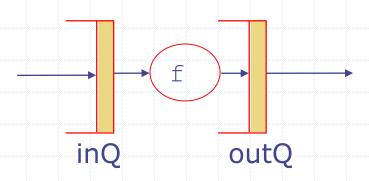

### Streaming a function using a FIFO with guarded interfaces

```

rule stream;

if(inQ.notEmpty && outQ.notFull)

begin outQ.enq(f(inQ.first)); inQ.deq; end

endrule

```

```

rule stream (inQ.notEmpty && outQ.notFull);

outQ.enq(f(inQ.first)); inQ.deq;

endrule

```

The implicit guards of the method call are sufficient here

# Switch using FIFOs with guarded interfaces

```

redQ

switch

greenQ

rule switch;

if (inQ.notEmpty)

if (inQ.first.color == Red) begin<sub>1</sub>

if (redQ.notFull) begin<sub>2</sub>

All the red

redQ.enq(inQ.first.value); inQ.deq;

stuff can be

end<sub>2</sub>

deleted

end<sub>1</sub>

else begin,

if (greenQ.notFull) begin,

greenQ.eng(inQ.first.value); inQ.deg;

end,

end<sub>3</sub>

endrule

http://csg.csail.mit.edu/6.175

L05-6

September 15, 2017

```

# Switch using FIFOs with guarded interfaces

```

inQ redQ switch greenQ

```

```

rule switch;

if (inQ.first.color == Red) begin

redQ.enq (inQ.first.value); inQ.deq;

end else begin

greenQ.enq(inQ.first.value); inQ.deq;

end

endrule

```

What is the implicit guard?

inQ.notEmpty ? (inQ.first.color == Red ? redQ.notFull

: greenQ.notFull)

: False

http://csg.csail.mit.edu/6.175 L05-7

# Switch using FIFOs with guarded interfaces

```

inQ redQ redQ greenQ

```

```

rule switch;

if (inQ.first.color == Red) begin

redQ.enq (inQ.first.value); inQ.deq;

end else begin

greenQ.enq(inQ.first.value); inQ.deq;

end

inQ.deq;

endrule

```

Does this code still work?

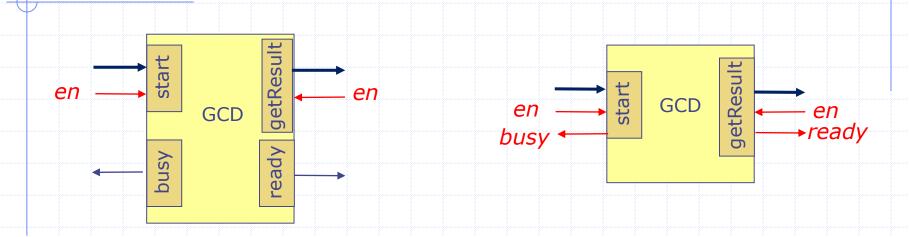

## GCD with and without guards

Interface without guards

Interface with guards

```

interface GCD;

method Action start (Bit#(32) a, Bit#(32) b);

method ActionValue#(Bit#(32)) getResult;

-method Bool busy;

-method Bool ready;

endinterface

```

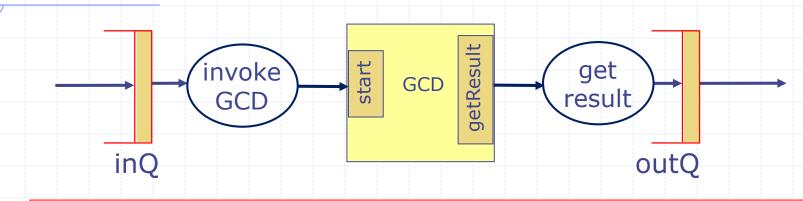

### Using GCD module with guarded interfaces

```

rule invokeGCD;

gcd.start(inQ.first); inQ.deq;

endrule;

```

```

rule getResult;

let x <- gcd.getResult; outQ.enq(x);

endrule;</pre>

```

A rule can be executed only if guards of all of its actions are true

http://csg.csail.mit.edu/6.175 L05-10

### GCD with guarded interfaces

implementation

```

interface GCD;

module mkGCD (GCD);

method Action start

Reg#(Bit#(32)) x <- mkReg(0);

(Bit#(32) a, Bit#(32) b);

Reg#(Bit#(32)) y <- mkReg(0);

method ActionValue (Bit# (32))

Req#(Bool) busy <- mkReq(False);</pre>

getResult;

endinterface

rule gcd;

if (x >= y) begin x \le x - y; end //subtract

else if (x != 0) begin x <= y; y <= x; end //swap

endrule

method Action start(Bit#(32) a, Bit#(32) b) if (!busy);

x \le a; y \le b; busy \le True;

endmethod

method ActionValue (Bit#(32)) getResult if (x==0);

busy <= False; return y;</pre>

endmethod

endmodule

```

Assume  $b \neq 0$

L05-11

September 15, 2017 http://csg.csa

http://csg.csail.mit.edu/6.175

#### Guards vs Ifs

```

method Action enq(t x) if (!v);

v <= True; d <= x;

endmethod</pre>

```

guard is !v; enq can be applied only if v is false

#### versus

```

method Action enq(t x);

if (!v) begin v <= True; d <= x; end

endmethod</pre>

```

guard is True, i.e., the method is always applicable.

if v is true then x would get lost;

bad

### Pipelining combinational circuits

### Pipelining Combinational Functions

- Lot of area and long combinational delay

- Folded or multi-cycle version can save area and reduce the combinational delay but throughput per clock cycle gets worse

- Pipelining: a method to increase the circuit throughput by evaluating multiple inputs

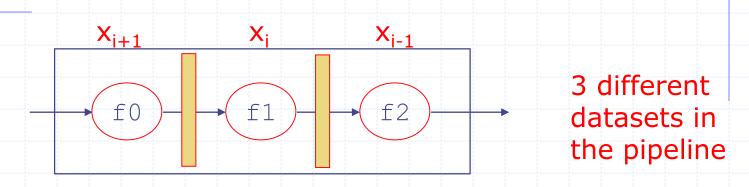

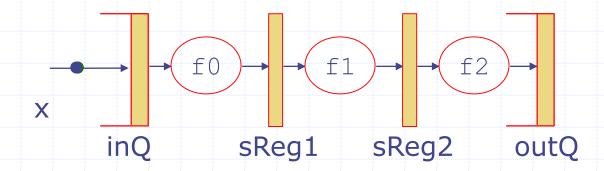

### Inelastic vs Elastic pipeline

Inelastic: all pipeline stages move synchronously

Elastic: A pipeline stage can process data if its input FIFO is not empty and output FIFO is not Full

Most complex processor pipelines are a combination of the two styles

September 15, 2017 http://csg.csail.mit.edu/6.175 L05-15

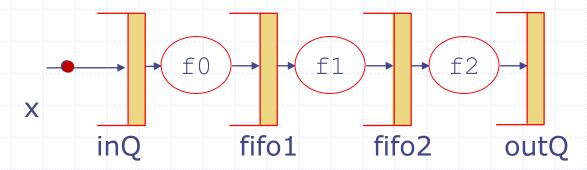

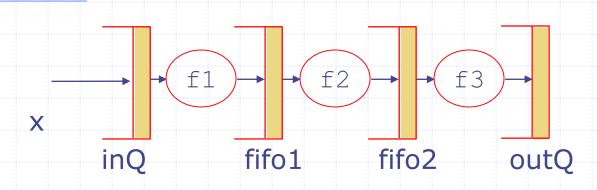

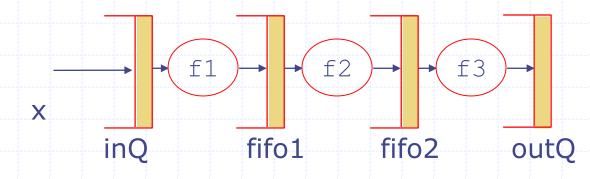

### Elastic pipeline

Use FIFOs instead of pipeline registers

no need for valid bits

- When can stage1 rule fire?inQ has an element

- fifo1 has space

- Can tokens be left in the pipeline?

No

- Can these rules execute concurrently?

### Elastic pipeline

- If these rules cannot execute concurrently, it is hardly a pipelined system

- When can rules execute concurrently?

- What hardware is synthesized to execute rules concurrently?

### Multi-rule Systems

#### Repeatedly:

- Select a rule to execute

- Compute the state updates

- Make the state updates

Non-deterministic choice; User annotations can be used in rule selection

One-rule-at-a-time-semantics: Any legal behavior of a Bluespec program can be explained by observing the state updates obtained by applying only one rule at a time

However, for performance we execute multiple rules concurrently whenever possible

stay tuned ...